Começando pelo básico, o que a arquitectura big.LITTLE significa é a criação de uma solução que consegue usar dois tipos de processadores, ou dois tipos de núcleos, sendo um deles específico para extrair o máximo desempenho do sistema, e outro que garanta um desempenho adequado, mas que permita reduzir significativamente o consumo energético. Esta tecnologia foi inicialmente desenvolvida para a família de núcleos Cortex-A da ARM, utilizados nos processadores dos SoC (System-on-Chip) utilizados em dispositivos móveis. Isto deu a possibilidade de manter o consumo energético baixo em situações banais, como ver o e-mail, navegar na Internet ou responder a mensagens, sem prejudicar o desempenho do sistema necessário para utilizações intensivas, como jogos e gravação de vídeo em altas resoluções (4K e 8K).

Estrutura

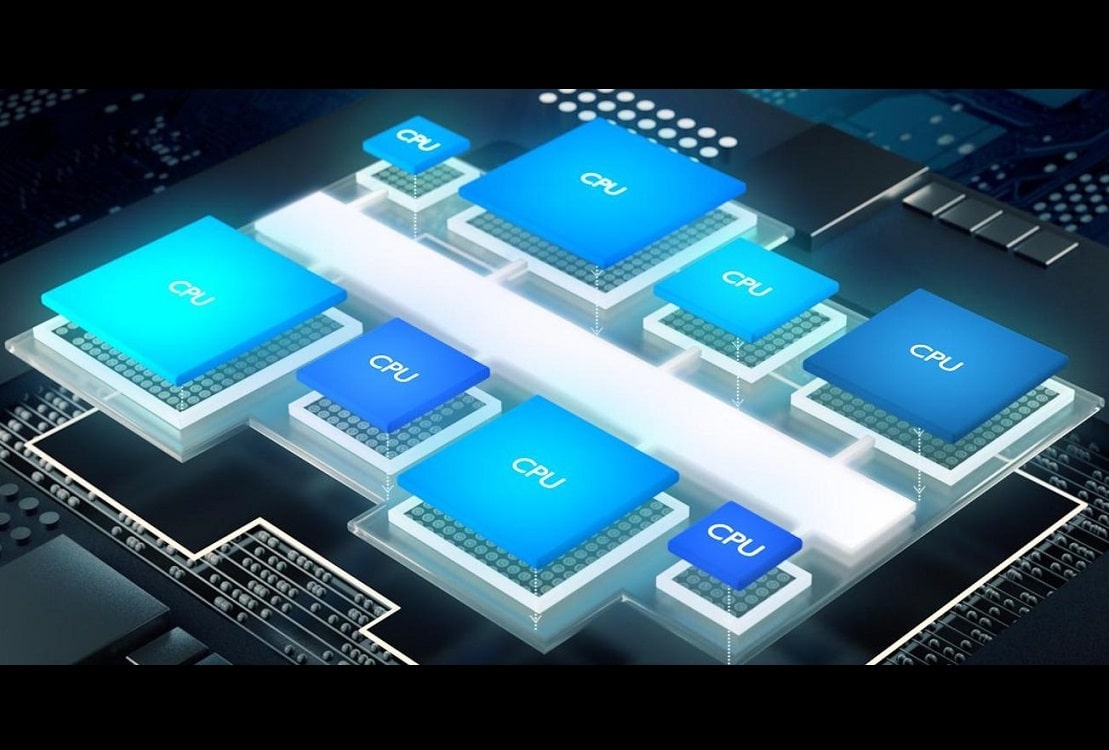

A estrutura de um processador que utiliza a arquitectura big.LITTLE da ARM é muito simples: temos um módulo com núcleos de baixo consumo energético (como os Cortex-A55), uma memória cache L1 interna por núcleo e uma cache L2 partilhada. Há ainda um módulo similar, mas com núcleos de elevado desempenho (Cortex-A75, por exemplo), também eles com cache L1 dedicada e cache L2 partilhada.

Estes módulos usam dois tipos de canais de comunicação entre si, os CoreLink GIC-400 e CCI-400. O primeiro é responsável pela gestão de tarefas entre os módulos, desligando-os sempre que não sejam necessários; o segundo permite gerir a coerência da cache, ou seja, garante que a informação presente na memória cache de um núcleo/módulo é consistente com a informação presente na cache dos restantes núcleos/módulos.

Isto é particularmente importante, se tivermos em conta que o sistema, sempre que precisa de aceder a qualquer tipo de dados, “comunica” em primeiro lugar com memória cache (L1 e L2), antes de “falar” com memória do dispositivo e, depois, com o sistema de armazenamento de dados (ROM).

Aplicações e futuro

A primeira vez que esta arquitectura foi aplicada foi nos núcleos Cortex-A15 e Cortex-A7, utilizados nos SoC da Samsung Exynos 5410 e 5420, que “alimentaram” os smartphones Samsung Galaxy S4 e Galaxy Note 3. Naturalmente que, enquanto primeira solução, a ARM acabou por a evoluir, dando assim origem à arquitectura DynamIQ, que permite simplificar e integrar melhor os diferentes módulos, eliminando as elevadas latências, devido à necessidade da ligação GIC-400, que permitia a comunicação entre os diferentes módulos. Com a arquitectura DynamIQ, os módulos, que podem agora usar até oito núcleos cada, passam a comunicar directamente dentro do mesmo substrato, sendo acrescentada uma memória cache L3 adicional, partilhada por todos os módulos.

A arquitectura big.LITTLE da ARM acabou por se tornar o padrão de todas as actuais (e futuras) arquitecturas híbridas, como os novos processadores Intel Alder Lake-S e os populares SoC Apple da série A e M.