O lançamento dos novos processadores Alder Lake, pode ter sido um grande sucesso para a empresa, mas a Intel tem grandes ambições para o futuro. De acordo com uma patente publicada recentemente, a empresa pode usar transístores ‘stacked forksheet’ para manter viva a Lei de Moore.

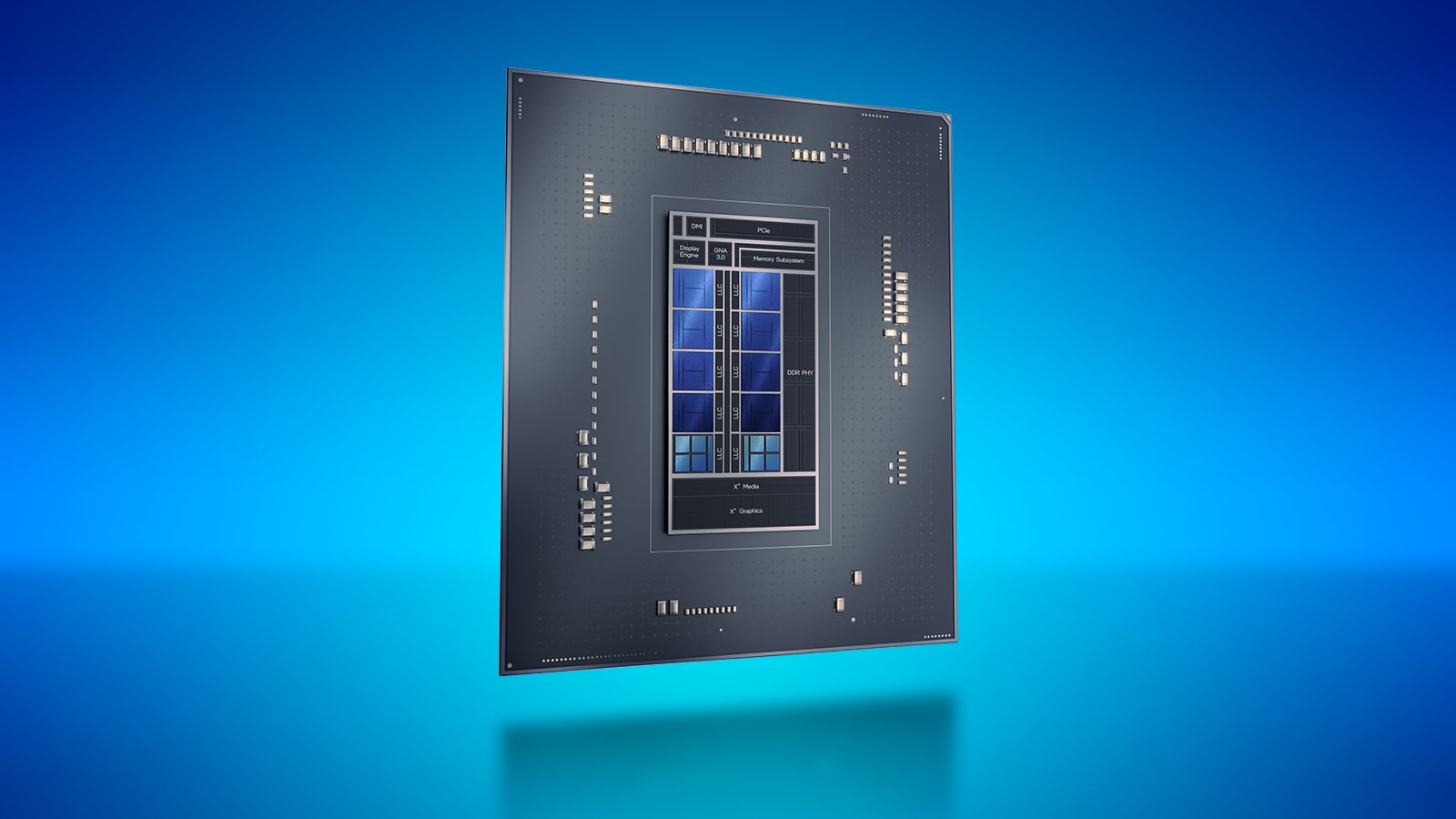

Apesar dos recentes sucessos no mercado dos processadores para PC, a Intel pode precisar de alguns anos para recuperar o lugar que já ocupou no mercado dos semicondutores. Nos últimos meses, a empresa tem mostrado novos processos de fabrico e embalagem que vai lançar a médio prazo, incluindo novos transístores 3D, integração Foveros ‘logic-to-logic’ e a Embedded Multi-Die Interconnect Bridge (EMIB).

Contudo, o aspecto mais interessante no objectivo da Intel em tornar-se líder neste campo pode ser visto através das suas últimas patentes. Uma delas, descreve o que a Intel chama ‘stacked forksheet transistor’, que pode ser a chave para manter viva a Lei de Moore, mesmo utilizando processos de fabrico abaixo do dos 3 nm.

A patente em si não menciona nenhuns melhoramentos de Power-Performance-Area (PPA), mas revela a visão da Intel de uma arquitectura CMOS de empilhamento vertical que pode permitir densidades de transístores mais altas nos designs de futuros chips. Estes melhoramentos aumentam bastante a complexidade do fabrico, por isso a Intel diz que aumentar a miniaturização requer um equilíbrio entre as dimensões e o espaçamento entre os componentes.

A Intel está a explorar a ideia de usar ‘nano fitas’ de transístores que podem ser empilhados e separados entre entre por uma película de germânio que serve como isolador. Isto permitiria à empresa integrar transístores PMOS e NMOS em espaços mais pequeno sem afectar o seu funcionamento. No mínimo, pode levar a uma redução de 50% da área de um dispositivo CMOS, duplicando assim a densidade de circuitos integrados desenvolvidos no futuro.

Em 2019, a Imec, uma empresa sediada na Bélgica, já explorou um conceito semelhante, chamado CFET e simulou processos de fabrico de chips de 2 nm. Os resultados demonstraram melhorias de 24% na eficiência energética e uma redução de 20% na área ocupada. Este processo pode reduzir em 30% a área ocupada pelos componentes da memória cache nos processadores.

A TSMC, diz que o seu processo de fabrico de 3 nm vai oferecer entre 10 e 15 % de melhorias no desempenho e cerca de 30 % de eficiência energética, quando comparado com o processo de fabrico de 5 nm da empresa. O processo de 3 nm, também permite um aumento de 70% de densidade de componentes nos núcleos dos CPU e um aumento de densidade de 20% no que respeita às SRAM.